# **CONTROLE PID DE UM SISTEMA VIBRATÓRIO BASEADO NO PROCESSADOR DSP TMS320.**

**Juan Carlos Villadiego Torres**

[jvilladiego@mecanica.ufu.br](mailto:jvilladiego@mecanica.ufu.br)

Universidade Federal de Uberlândia - FEMEC - Faculdade de Engenharia Mecânica. Av. João Naves de Ávila, 2160 - Bloco M - Sala 212, Fone: (34) 3239 4148/4192/4150 CEP 38400-9002 Uberlândia - MG

**José Francisco Ribeiro**

[jribeiro@mecanica.ufu.br](mailto:jribeiro@mecanica.ufu.br)

Universidade Federal de Uberlândia - FEMEC - Faculdade de Engenharia Mecânica. Av. João Naves de Ávila, 2160 - Bloco M - Sala 212, Fone: (34) 3239 4148/4192/4150 CEP 38400-9002 Uberlândia – MG

**Resumo.** *A despeito das inúmeras técnicas de sintonia de controladores PID encontradas na literatura, nenhuma técnica se mostrou razoavelmente eficiente quando aplicada a problemas de controle de vibrações mecânicas em sistemas muito pouco amortecidos, sem atraso e com vários graus de liberdade. Este trabalho apresenta uma estratégia de sintonia de controladores PID para estes sistemas, na perspectiva da implantação da mesma em processadores digitais de sinais de baixo custo. São desenvolvidos no trabalho os procedimentos analíticos e apresentados resultados experimentais da estratégia proposta. O algoritmo de sintonia é implementado num processador DSP TMS320LF2407A e os ensaios experimentais são conduzidos num sistema vibratório de um grau de liberdade.*

**Palavras-chave:** Controlador PID, Vibrações, DSP, Identificação.

## **1. INTRODUÇÃO**

As técnicas clássicas de projeto de controle de sistemas dinâmicos requerem, em sua maioria, o conhecimento da função de transferência da planta. Estimulando a planta a partir de entradas conhecidas e operando com os sinais de entrada e saída é possível obter um modelo para a função de transferência, (Phillips, 1997) e então projetar o controlador. Neste trabalho é aplicada uma variante do método do relé, devido a Aström *et al.* (1988), que procura identificar e ajustar de forma automática os parâmetros de um controlador PID. Tal procedimento é construído na perspectiva da sua implantação em processadores digitais de sinais (DSPs).

Os DSPs são microprocessadores especialmente projetados para processar altos volumes de sinais digitais, o que envolve estruturas especiais de hardware e software para filtrar sinais, calcular transformadas, operar convoluções, etc. O processamento digital de sinais iniciou nos anos 60 com o surgimento dos primeiros computadores que, devido aos elevados custos, eram usados em 4 áreas vitais: radar e sonar, exploração de petróleo, exploração do espaço e nas imagens médicas. Foram nos anos 80 e 90, com a evolução da microeletrônica e o surgimento de novas tecnologias de fabricação de circuitos integrados, que novas aplicações para o processamento digital de sinais tornaram-se possíveis, (Smith, 1999).

Em 1982 a TI (*Texas Instruments*) introduziu no mercado seu primeiro DSP programável de propósito geral, o TMS32010 que operava a 5 MIPS (Milhões de Instruções por Segundo). Em 1988 a TI introduziu o primeiro DSP ponto flutuante da indústria, o TMS320C3x para aplicações tais como correio de voz, fax gráficos 3D, e escaneres de código de barras, ao mesmo tempo em que o TMS320C1x se convertia no primeiro DSP dirigido à ajuda auditiva. Em 1989, o TMS320C5x com 28 MIPS, equivalente de 2 a 4 vezes melhor desempenho do que qualquer outro do tipo ponto fixo, é usado em telefonia celular, modems de alta velocidade, impressoras, e copiadoras. Em 1992 a área de DSPs foi o setor com maior crescimento no mercado da eletrônica automotiva. A grande capacidade de cálculo matemático em tempo real dos DSPs permitiu a sua utilização em sistemas de suspensão ativa, de controle em motores de combustão, de trajetórias inteligentes, de freios antibloqueios (ABS), etc. Em 1995 mais de 95% de todos os HD (*hard disk*) de alto desempenho empregam um DSP da família TMS320.

Neste trabalho é utilizado, na síntese do controlador, um DSP da *Texas Instruments*, o TMS320LF2407, dadas a sua versatilidade e a facilidade de desenvolvimento de software e hardware, hoje disponíveis.

## 2. FAMÍLIA DOS DSP TMS320

A família dos DSP TMS320 tem uma arquitetura especificamente projetada para processamento em tempo real e envolve: (a) processadores digitais de ponto fixo, (b) processadores digitais de ponto flutuante, (c) multi-processadores digitais e (d) controladores digitais de ponto fixo. A Tabela (1) mostra as gerações das famílias desenvolvidas pela TI.

Tabela 1. Gerações das famílias dos DSPs.

| Família                 | Gerações             |

|-------------------------|----------------------|

| DSPs Ponto fixo         | C1X, C2X, C20X, C24X |

| DSPs Ponto flutuante    | C3X, C4X             |

| DSPs Multiprocessadores | C8X                  |

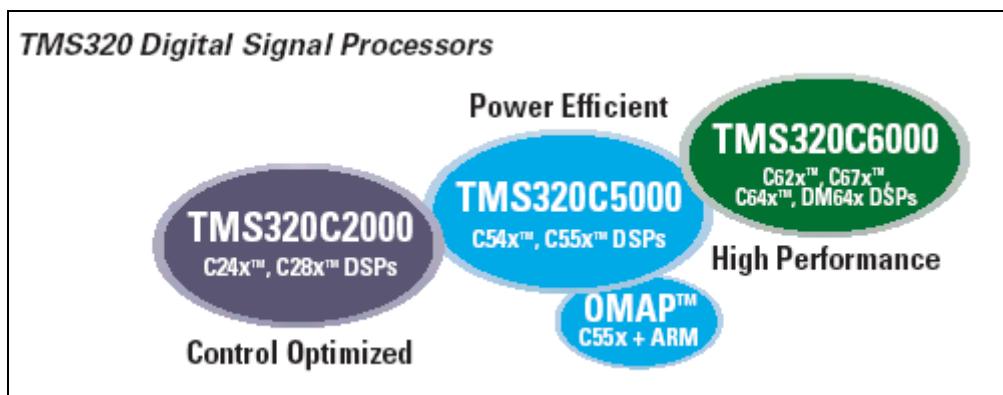

Como se observa na Fig. (1) as gerações C24X, C28x da plataforma C2000 são otimizadas para aplicação na área de controle. As plataformas C54X e C55X estão encaminhadas ao uso eficiente de potência. Por último, as plataformas C2X, C67X, C64X e DM64X são projetadas para aplicações de alto desempenho.

Figura 1. Gerações dos DSPs. (fonte: site [www.ti.com](http://www.ti.com))

## 2.1. DESCRIÇÃO DA PLACA EZDSP 2407

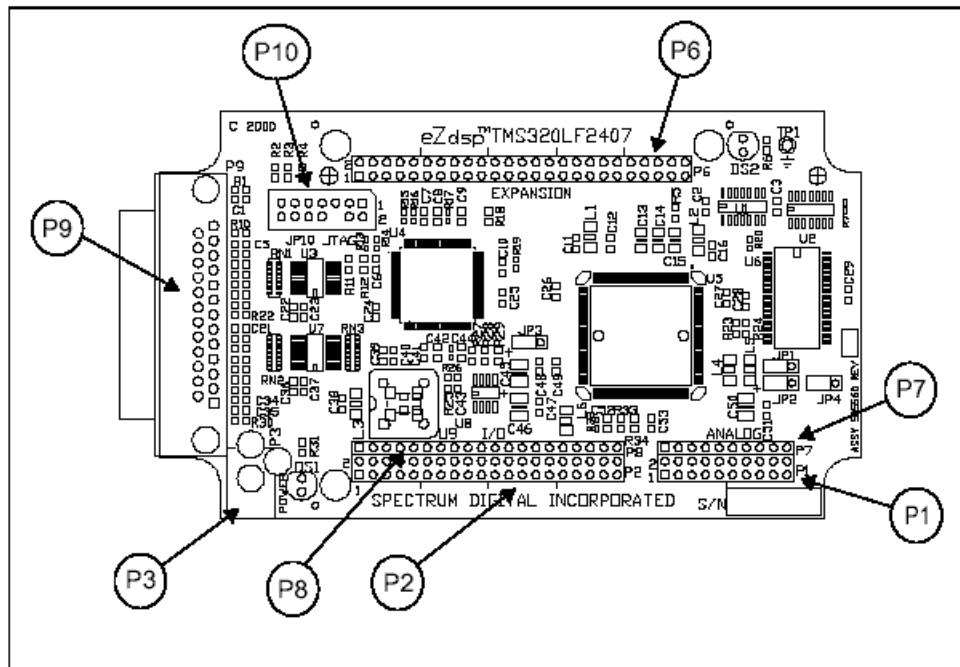

Uma das ferramentas de desenvolvimento de produtos baseados nos DSPs, comercializadas pela TI, e utilizada neste trabalho é a placa eZdsp 2407, Fig. (2). Tal placa, uma vez conectada à porta paralela de um PC, permite de uma forma bastante eficiente e rápida o desenvolvimento, teste e avaliações de aplicativos de controle de processos. A eZdsp 2407 usa o processador digital TMS320LF2407 e tem oito conectores de I/O conforme a Tab. (2).

Figura 2. Identificação de portas na placa eZdsp 2407.

Tabela 2. Função dos conectores da placa eZdsp 2407.

| Porta | Função                           |

|-------|----------------------------------|

| P1/P7 | Interface analógica.             |

| P2/P8 | Interface de entrada e saída I/O |

| P3    | Conector de potência, 5V, 1A.    |

| P6    | Expansão de entrada e saída I/O  |

| P9    | Porta paralela                   |

| P10   | Interface JTAG                   |

## 2.2. ESPECIFICAÇÕES TÉCNICAS DO DSP TMS320LF2407A

O DSP instalado na placa é um chip de 144 pinos, com memória *flash* incorporada e capaz de operar entre  $-40^{\circ}\text{C}$  até  $85^{\circ}\text{C}$ . As principais especificações técnicas do DSP utilizado são:

- Carcaça da família dos DSP TMS 320C2XX.

- Tempo do ciclo de instrução de 25ns devido a que pode processar até 40 MIPS (Milhões de Instruções por segundo).

- Memória *flash* de até 32K palavras de 16 bits dividida em 4 setores de 4K, 12K, 12K, 4K.

- Memória RAM de até 2.5K palavras de 16 bits divididas em 544 palavras de dados e até 2K palavras de programa (de acesso simples).

- Não tem memória ROM.

- Interface de memória externa de 192K palavras de 16 bits divididas em 64K de programa, 64K de dados e 64K de entrada e saída (I/O).

- Tem dois módulos gerenciadores de eventos EVA e EVB onde cada um deles inclui:

- 02 contadores (*timers*) de propósito geral de 16 bits.

- 08 canais PWM (Modulação de largura de pulso).

- 03 unidades de captura de eventos externos.

- Módulo *Watchdog*.

- Módulo Análogo-Digital (ADC) de 10 bits, 16 canais e tempo conversão de 375ns (15 ciclos de máquina).

- Módulo CAN (*Controller Area Network*) 2.0B.

- Interface de comunicação *serial* (SCI).

- Interface periférica *serial* de 16 bits.

- 40 pinos compartilhados de entrada/saída (I/O) digital.

- 5 interrupções externas (*Power drive protection, reset*, dois interrupções cobertas).

- Tensão de alimentação de 3.3V.

### 3. MÉTODO DE SINTONIA DE PID UTILIZADO

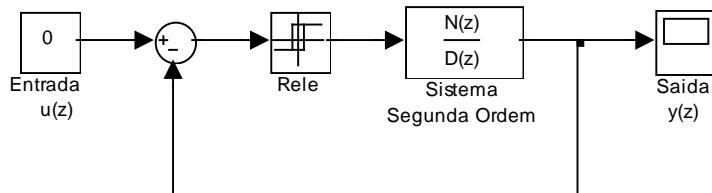

As pesquisas na área de controladores PID têm evoluído muito nos últimos anos, (Preface, 2001) e particularmente um segmento de destacado interesse é aquele da sintonia automática dos ganhos do controlador. Em (Cardoso, 2001) é apresentada uma proposta de sintonia, baseada no método do relé, originalmente apresentado por Aström *et al.* (1988). No teste do relé, Fig. (3), caso o sistema seja relé estabilizável Aström *et al.* (1988) o mesmo é levado a oscilar numa das suas freqüências naturais e a análise das condições de oscilação permite derivar os parâmetros da planta naquela freqüência de oscilação. Supõe-se conhecida, por não apresentar dificuldades de averiguação, o comportamento da planta para uma entrada constante (DC).

Figura 3. Identificação do sistema usando o método do relé realimentado.

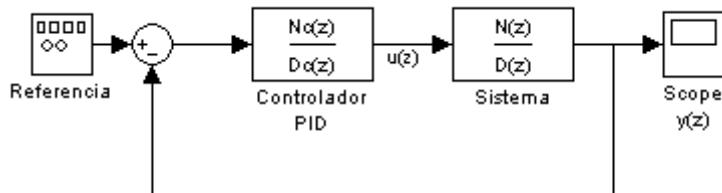

Supondo que se tenha como requisito de projeto um certo comportamento em freqüência para o conjunto planta+controlador mostrado na Fig. (4). O problema é encontrar os ganhos do controlador PID de sorte que o requisito posto seja atendido.

Figura 4. Controlador + sistema com sinal de referencia.

Isto pode ser expresso matematicamente conforme a Eq.(1):

$$G_c(s) * G_p(s) = G_{ref}(s) \quad (1)$$

onde:

$Gc(s)$ : Função transferência do controlador.

$Gp(s)$ : Função transferência da planta.

$Gref(s)$ : Função transferência do sistema de referencia.

A Eq. (1) deve particularmente ser respeitada nas freqüências conhecidas, ou seja, na freqüência de oscilação do relé ( $w_c$ ) e no nível DC ( $w_{dc}$ ), Eq. (2) e Eq. (3). Assim:

$$\left( Kp + Kd \cdot w_c \cdot j + \frac{Ki}{w_c j} \right) (a_p + b_p \cdot j) = a_r + b_r \cdot j \quad (2)$$

$$\left( Kp + Kd \cdot w_{dc} \cdot j + \frac{Ki}{w_{dc} j} \right) (c_p + d_p \cdot j) = c_r + d_r \cdot j \quad (3)$$

onde:

$Kp$ : Constante proporcional do controlador PID.

$Ki$ : Constante integral do controlador PID.

$Kd$ : Constante derivativa do controlador PID.

$w_c$ : Freqüência natural do sistema.

$w_{dc}$ : Freqüência estática do sistema.

$a_r$ : Parte real da função de transferência desejada na freqüência natural.

$b_r$ : Parte imaginaria da função de transferência desejada na freqüência natural.

$c_r$ : Parte real da função de transferência desejada em baixa freqüência.

$d_r$ : Parte imaginaria da função de transferência desejada em baixa freqüência.

$j$ : Número imaginário.

Supondo que em baixas freqüências não há defasagem entre a saída e a entrada da planta então o termo  $d_p$  é nulo na Eq. (3). Por sua vez, admitindo ainda que em baixa freqüência o sistema desejado apresenta uma defasagem de  $90^\circ$ , ou seja  $c_r = 0$  na Eq. (3). As equações acima podem ser reescritas na forma da Eq. (4):

$$\begin{bmatrix} a_p & \frac{b_p}{w_c} & -b_p \cdot w_c \\ b_p & -\frac{a_p}{w_c} & a_p \cdot w_c \\ 0 & -\frac{c_p}{w_{dc}} & c_p \cdot w_{dc} \end{bmatrix} \begin{bmatrix} Kp \\ Ki \\ Kd \end{bmatrix} = \begin{bmatrix} a_r \\ b_r \\ d_r \end{bmatrix} \quad (4)$$

A solução do sistema de equações acima em termos dos parâmetros do controlador depende do conhecimento de  $a_p$ ,  $b_p$  e  $c_p$ . Tais parâmetros estão associados ao valor da função de transferência da planta nas freqüências  $w_c$  e  $w_{dc}$ . O parâmetro  $c_p$  é a razão entre a magnitude do sinal da saída e do sinal da entrada, quando esta é do tipo degrau. Ou seja:

$$c_p = \frac{y_{dc}}{u_{dc}} \quad (5)$$

Quando a planta é excitada por um sinal senoidal na sua primeira freqüência natural a saída fica  $90^\circ$  atrasada em relação à entrada, o que resulta num  $a_p = 0$  e  $b_p$  negativo expresso por Cardoso (2001):

$$b_p = -\frac{y_{RMS}}{u_{RMS}} \quad (6)$$

onde  $y_{RMS}$  é o valor médio quadrático do sinal de saída e  $u_{RMS}$  o valor médio quadrático do sinal de entrada.

Pode-se assim resumir o procedimento de sintonia do PID:

Passo 01: realiza-se o ensaio do relé realimentado, conforme Fig. (3), e identifica-se a freqüência natural de oscilação.

Passo 02: com o sistema em malha aberta aplica-se um sinal senoidal na entrada na freqüência identificada no passo anterior e, a partir dos valores rms da saída e da entrada, calcula-se o parâmetro  $b_p$ , conforme Eq. (6).

Passo 03: aplica-se um sinal DC na planta e observa-se a saída. O parâmetro  $c_p$  é calculado conforme a Eq. (5).

Passo 04: calcula-se os parâmetros  $a_r$ ,  $b_r$  e  $d_r$  de acordo com as especificações desejadas para as funções de transferência na freqüência natural e no nível DC.

Passo 05: calcula-se os parâmetros do controlador resolvendo a Eq. (4).

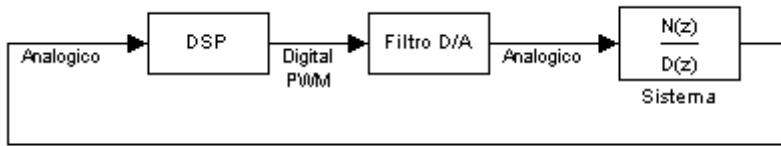

O uso da placa eZdsp 2407 exige que se opere com os sinais de entrada e saída, adequando-os às condições de operação. O sinal de controle é gerado na forma PWM, que para ser adequadamente aplicado ao sistema precisa ser convertido num sinal analógico o que é feito por um filtro analógico de 5<sup>a</sup> ordem do tipo Butterworth. O sinal do sensor é também por sua vez condicionado segundo as restrições de entrada dos canais analógicos da placa.

A Fig. (5) ilustra a utilização de dos dois canais no processador DSP, onde o sinal de entrada procedente do sensor chega num dos 16 canais analógicos disponíveis nas portas P1 e P7 da Fig.(2) cuja faixa de trabalho é de 0V até 3.3V e para o sinal de saída se usa um dos 8 canais PWM da porta P2 da Fig. (2).

Figura 5. Diagrama de blocos da entrada e saída de sinais no DSP.

#### 4. RESULTADOS EXPERIMENTAIS

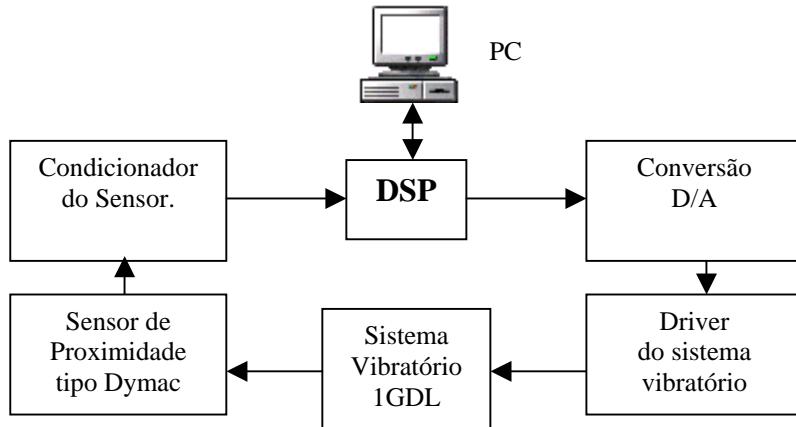

Na obtenção dos resultados experimentais se trabalhou utilizando um sistema de 1 GDL, constituído por uma mesa suportada por 4 laminas de aço inoxidável e cujo comportamento dinâmico se assumiu unidimensional. Desconsideraram-se eventuais deformações e/ou deslocamentos verticais da mesa. O atuador da mesa é constituído por duas bobinas dispostas em direções opostas que induzem uma força eletromagnética na mesa. Este sistema de bobinas é governado por um driver e alimentado por uma fonte de tensão estabilizada. Na Fig. (6) se apresenta o diagrama de blocos da instrumentação utilizada.

Figura 6. Instrumentação usada no laboratório.

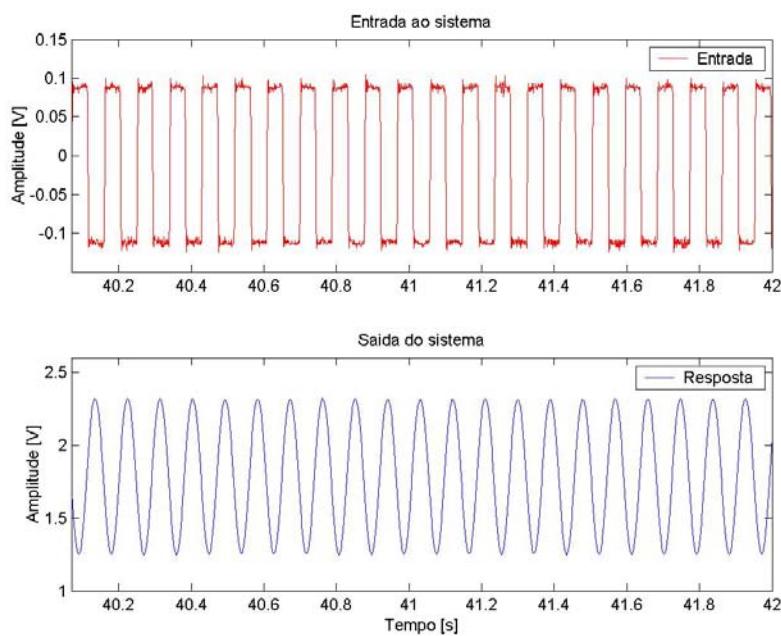

Utilizando o método do relé, no sistema especificado, a freqüência identificada foi de 11.5 hz. O comportamento do sistema neste ensaio é apresentado na Fig. (7).

Figura 7. Método do rele aplicado ao sistema.

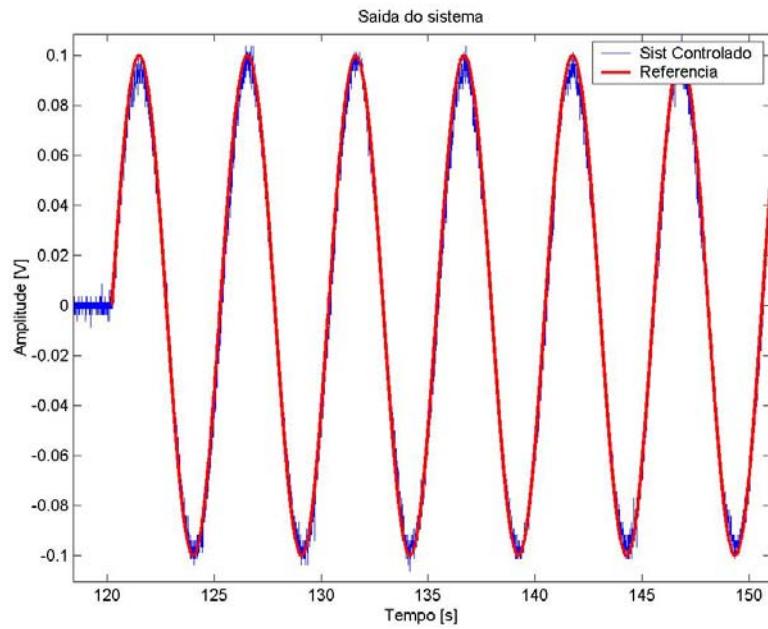

O ajuste do PID foi realizado conforme descrito anteriormente, sendo obtido os seguintes resultados para os ganhos  $K_p = -0.0212$ ,  $K_i = 14.3487$  e  $K_d = 0.0040$ . O sistema foi testado, observando a sua capacidade em acompanhar um sinal senoidal na freqüência de 0.2hz e com uma amplitude de 0.2 Volts pico-pico. Os resultados são mostrados na Fig. (8).

Figura 8. Resposta do sistema a uma referencia senoidal com 0.2hz de freqüência.

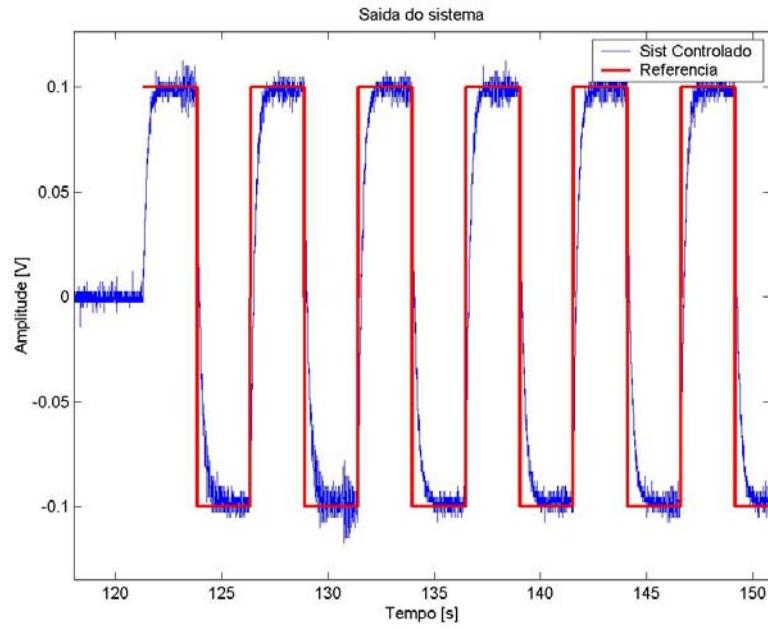

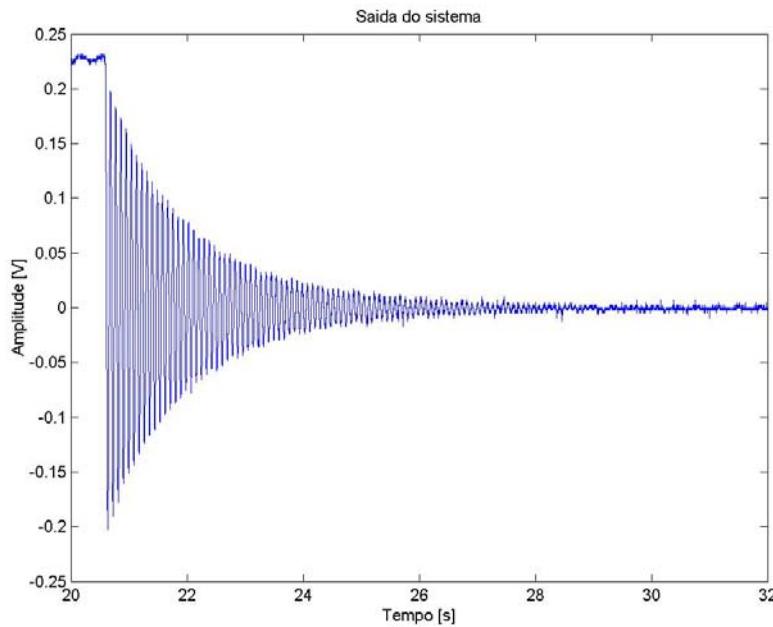

Um segundo teste foi efetuado, agora tendo como referência uma onda quadrada com o mesmo valor de freqüência do caso anterior e obtiveram-se os resultados da Fig. (9). Neste caso o sistema responde com um tempo de acomodação de 1.04s, muito menor do que no caso livre, Fig. (10), onde acomoda em 12s. Nestes dois casos o tempo de amostragem foi de 1ms.

Figura 9. Resposta do sistema a uma referencia tipo onda quadrada com 0.2hz de freqüência.

Ensaios de sinais de referência com diferentes amplitudes para o caso de onda quadrada e do tipo senoidal, têm comportamentos idênticos aos apresentados.

A Fig. (10) ilustra o sinal de saída do sistema onde se observa seu comportamento livre quando se retira dele uma entrada degrau de 0.5V.

Figura 10. Comportamento livre do sistema.

## 5. CONCLUSÕES

A metodologia de sintonia PID mostrou-se eficiente e capaz de ser implementada em DSPs de baixo custo e elevada performance, uma vez que podem ser obtidos mil destes micro-chips por menos de 30 reais [9], o que equivale a um valor desprezível quando comparado com valor da planta. Tais características podem ser aproveitadas em aplicações industriais, onde este tipo de controladores tem uma aceitação cada vez maior.

Os módulos de conversão analógica-digital ADC e de geração de sinais tipo PWM que oferece o DSP320LF2407 facilita grandemente a utilização deste equipamento na área de controle digital.

As ferramentas de desenvolvimento mostraram-se bastante eficientes e resta para o futuro discutir a performance do sistema em aplicações mais sofisticadas, tipo multi-canais, onde restrições de processamento são seguramente mais restritivas.

## 6. AGRADECIMENTOS

Ao Laboratório de Sistemas Mecânicos LSM da UFU e ao CNPq pelo apóio financeiro.

## 7. REFERÊNCIAS

- Berkeley Design Technologies, "DSP Markets", 1999. eecs\_488\_dsp.pdf.

- Cardoso, P. M., Dissertação de Mestrado – UFU, 2002, "Estudo, proposta e avaliação de novas metodologias de sintonia automática de controladores PID baseadas no ensaio do relé realimentado".

- Hagglund, T. e Aström, K. J., 1988, "Automatic Tuning of PID Controllers", Instruments Society of America.

- Phillips L., Charles; Royce D. Harbor, 1997, "Sistemas de Controle e Realimentacao", Makron Books. Brasil.

- Preface, 2001, "PID Control", Control Engineering Practice, Vol. 9, pp 1159-1161.

- Smith, Steven W., "The Scientist and Engineer's Guide to Digital Signal Processing", 2<sup>nd</sup> Edition, 1999.

- Spectrum Digital Inc., "eZdsp LF2407 Technical Reference", 2000.

Texas Instruments, “TMS320LF/LC240xA DSP Controllers Reference Guide”, System and Peripherals, 2001. spru357b.pdf.

Texas Instruments Inc., site: <http://focus.ti.com/docs/prod/folders/print/tms320lf2407a.html>.

## **8. DIREITOS AUTORAIS**

Os autores são os únicos responsáveis pelo conteúdo do material impresso incluído no seu trabalho.

## **PID CONTROL FROM A VIBRATING SYSTEM BASED ON A TMS320 DSP PROCESSOR**

*Abstract. Many of tuning methods for PID controllers were found on books, but any of them was efficient enough when applying in mechanical vibration control problems on low damper, no delay and many degrees of freedom systems. This work presents a tuning strategy for PID controllers for these systems, under the perspective of its application on low cost digital signal processors. Experimental results are presented using that strategy. Tuning algorithm was programmed on a TMS320LF2407A DSP processor and experimental tests were made in a one degree of freedom vibrating system .*

**Keywords.** *PID Control, Vibrations, DSP Processor, Identification.*